Volgens rapporten heeft Samsung Electronics voor het eerst ter wereld met succes een DRAM-werkwafer geproduceerd op basis van de 4F²-architectuur, waarmee de fysieke krimpgrens wordt doorbroken waar traditionele vlakke DRAM al lang mee te maken heeft. Naar verluidt heeft Samsung in februari van dit jaar dit 16Gb DRAM-prototype met 4F²-architectuur voor het eerst publiekelijk gedemonstreerd tijdens de ISSCC 2026-conferentie.

Samsung voltooide de waferproductie met behulp van het 10a-proces in maart en bevestigde de normale werking van de wafer door middel van karakteristieke tests. Deze prestatie is 's werelds eerste praktijk waarbij 4F²-celstructuur en verticale kanaaltransistortechnologie (VCT) worden geïntegreerd.

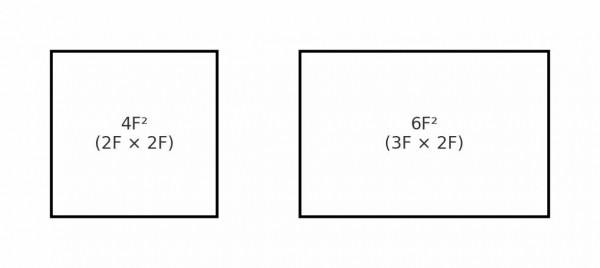

Technisch gezien reduceert de 4F²-architectuur de oppervlakte-eenheid van traditionele DRAM van 6F² naar een vierkante structuur van 2F×2F, wat theoretisch de capaciteit per oppervlakte-eenheid met 30% tot 50% kan verhogen, terwijl rekening wordt gehouden met de voordelen van snelheid en stroomverbruik.

Om deze structuur te realiseren heeft Samsung VCT-technologie geïntroduceerd om het transistorkanaal verticaal op te richten en de kanaallengte binnen het beperkte chipgebied te vergroten, waardoor het kortekanaaleffect en de lekkageproblemen waarmee traditionele planaire transistors tijdens het schalen worden geconfronteerd, effectief worden verlicht.

Aan de andere kant gebruikt Samsung inter-wafer hybride koperverbindingstechnologie om de geheugencelarray en randapparatuurcircuits op verschillende wafers te scheiden en ze vervolgens verticaal te stapelen om interconnectie met ultrahoge dichtheid te bereiken.

Het kanaalmateriaal is ook veranderd van traditioneel silicium naar indium gallium zinkoxide (IGZO) om lekstroom in krimpende cellen te onderdrukken.

In de toekomst kunnen DRAM-chips van dezelfde grootte met meer eenheden worden verpakt. Van terminalapparaten zoals dunne en lichte notebooks en smartphones wordt verwacht dat ze een grotere geheugencapaciteit en een snellere gegevensdoorvoer zullen bereiken, onder het uitgangspunt van een klein formaat en een laag stroomverbruik.

Samsung heeft hiervoor een duidelijke routekaart gepland: de ontwikkeling van 10a DRAM voltooien in 2026, kwaliteitstests uitvoeren in 2027 en overgaan naar massaproductie in 2028.

SK Hynix is van plan 4F²+VCT te introduceren op het 10b-knooppunt, terwijl Micron de bestaande ontwerproute handhaaft. Chinese fabrikanten zetten 3D DRAM rechtstreeks in vanwege EUV-beperkingen.